And generally speaking, when we are dealing with multiple inputs of the same kind, using vectors saves us a lot of complexity. The first one will be the SUM, and the second one will be the CARRY. And the output vectors will have two slots. We can easily assign two vectors, one to inputs and one to outputs.

Half adder truth table equation full#

The reason is that since we are using the truth table of the full adder, we have three inputs and two outputs. We will declare the entities as vectors.īut why? Why not declare each input/output separately?

Half adder truth table equation code#

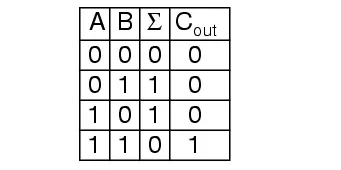

The entity-architecture declaration for the VHDL code of a full adder will have only one difference. Since this carry is not added to the final answer, the addition process is somewhat incomplete. The half adder gives out two outputs, the SUM of the operation and the CARRY generated in the operation.

0 kommentar(er)

0 kommentar(er)